In this problem, you will be asked questions pertaining to CAD techniques for the verification of digital circuits. A combinational circuit, such as the arithmetic-logic unit (ALU) of a microprocessor, might have 256 inputs. Conceptually, such a circuit performs a mapping from a space of  $2^{256}$  Boolean input values to Boolean output values. A truth table representing  $2^{256}$  input assignments is inconceivable; verifying the behavior of such a circuit would seem like an intractable problem. Digital circuit designers have succeeded in their endeavor with data structures such as binary decision diagrams and implicit techniques such as Boolean satisfiability (SAT).

#### Verification Problem

Suppose that you're newly hired at Intel and you think that you've come up with a better design for the ALU of their latest generation of microprocessors. You're convinced that your design is correct but you had better be sure. How can you check?

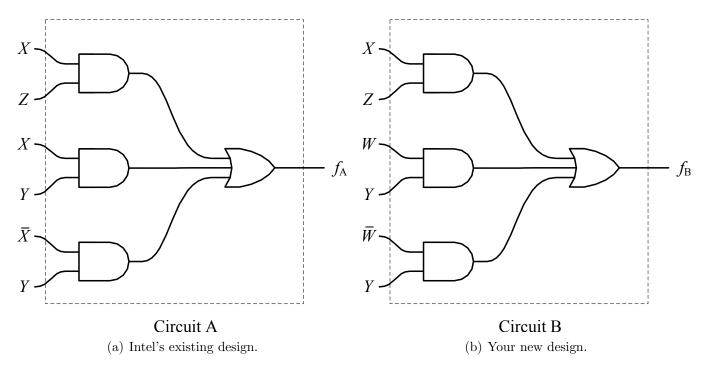

Call Intel's existing design Circuit A and your new design Circuit B. Suppose, for the purposes of this exam, that Circuits A and B are those shown in Figures 1(a) and 1(b), respectively. Call the Boolean functions computed by these circuits  $f_A$  and  $f_B$ , respectively.

Figure 1: Circuits to be verified.

# 1. Explicit Techniques (10 points)

Show, by evaluating  $f_A$  and  $f_B$  for all input combinations, that the two functions are equivalent.

# Solution

| W | X | Y | Z | $f_A$ | $f_B$ |

|---|---|---|---|-------|-------|

| 0 | 0 | 0 | 0 | 0     | 0     |

| 0 | 0 | 0 | 1 | 0     | 0     |

| 0 | 0 | 1 | 0 | 1     | 1     |

| 0 | 0 | 1 | 1 | 1     | 1     |

| 0 | 1 | 0 | 0 | 0     | 0     |

| 0 | 1 | 0 | 1 | 1     | 1     |

| 0 | 1 | 1 | 0 | 1     | 1     |

| 0 | 1 | 1 | 1 | 1     | 1     |

| 1 | 0 | 0 | 0 | 0     | 0     |

| 1 | 0 | 0 | 1 | 0     | 0     |

| 1 | 0 | 1 | 0 | 1     | 1     |

| 1 | 0 | 1 | 1 | 1     | 1     |

| 1 | 1 | 0 | 0 | 0     | 0     |

| 1 | 1 | 0 | 1 | 1     | 1     |

| 1 | 1 | 1 | 0 | 1     | 1     |

| 1 | 1 | 1 | 1 | 1     | 1     |

# 2. Algebraic Techniques (10 points)

Write algebraic expressions for  $f_A$  and  $f_B$ . Show, algebraically, that the two functions are equivalent.

## Solution

$$f_A = XZ + XY + \bar{X}Y$$

$$f_B = XZ + WY + \bar{W}Y$$

$$f_A = XZ + XY + \bar{X}Y$$

$$= XZ + XY(W + \bar{W}) + \bar{X}Y(W + \bar{W})$$

$$= XZ + WXY + \bar{W}XY + W\bar{X}Y + \bar{W}\bar{X}Y$$

$$= XZ + WY(X + \bar{X}) + \bar{W}Y(X + \bar{X})$$

$$= XZ + WY + \bar{W}Y$$

$$= f_B$$

### 3. Manipulation with XOR (15 points)

An useful representation in circuit verification is based on the AND and exclusive-OR (XOR) operations (with no negations). We will denote the XOR operation with  $\oplus$ . This representation is canonical: if we multiply out all parentheses, cancel pairs of identical terms, and sort the product terms, the resulting expression is unique. Accordingly, we'll call the representation XNF, for XOR Normal Form. (This isn't a standard term for the representation. It is sometimes known as the Reed-Muller form). For instance, for the function

$$f = a + b$$

the XNF representation is

$$f = a \oplus b \oplus ab.$$

For the function

$$g = \bar{x}_1 \bar{x}_2 \bar{x}_3 + \bar{x}_1 \bar{x}_2 x_3 + \bar{x}_1 x_2 \bar{x}_3,$$

the XNF representation is

$$g = 1 \oplus x_1 \oplus x_2 x_3 \oplus x_1 x_2 x_3.$$

The XNF representation has distinct advantages when manipulating expressions algebraically. Since it is canonical, we need not concern ourselves with simplifying the expressions, as we would working with sum-of-products or products-of-sums representations.

#### Problem

Show that the functions  $f_A$  and  $f_B$  from Question 2 are equivalent by putting them both in XNF.

#### Solution

$f_A = f_B = Y \oplus XZ \oplus XZY$

#### 4. Implicit Techniques (15 points)

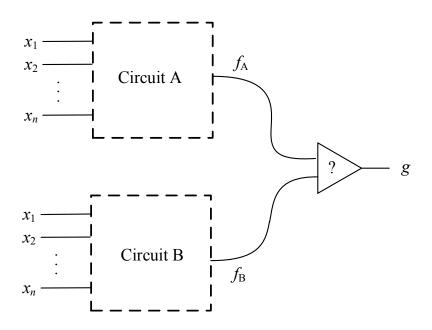

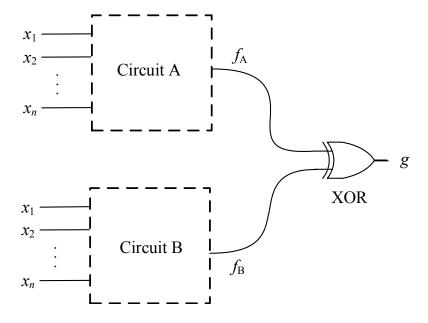

Explain how, conceptually, you can create a new circuit that will help you with the task of proving that Circuits A and B are equivalent. Specifically, how can you tie the outputs of the circuits together to create a new circuit that computes an output that is identically 0 (i.e., 0 for all input combinations) if and only if the two circuits compute the same Boolean function? Indicate what logical function should replace the question mark in Figure 2. Call the function implemented by the new circuit g.

Figure 2: A conceptual circuit for verifying whether Circuits A and B are equivalent.

Figure 3: Solution for Question 4.

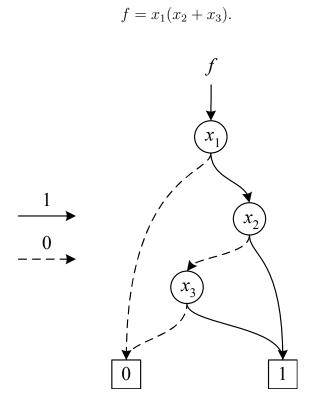

### 5. Binary Decision Diagrams (25 points)

First proposed in 1959 by Lee, binary decision diagrams (BDDs) were popularized in 1986 through a seminal paper by Bryant. A BDD consists of a directed graph in which nodes either have associated input variables or else are designated as a constant nodes ("0" or "1"). To evaluate a function one begins at a designated source node and follows a path dictated by the values of the variables until one arrives at one of the two constant nodes. The value of this constant node specifies the value of the function. An example is shown in Figure 4. The BDD in the figure represents the function

Figure 4: A binary decision diagram (BDD).

Although comparable in size to a truth table in the worst case, BDDs are surprisingly compact for many of the Boolean functions encountered in practice. This is due to the fact that BDDs can often be reduced in size by *collapsing* redundant nodes and *merging* equivalent nodes.

As with the XNF representation, the advantage of BDDs is that, for a given variable ordering, the representation is canonical.

## $\mathbf{Problem}$

Draw reduced BDDs for the function  $f_A = f_B$  in Question 2. What will the reduced BDD be for the function g in Question 4?

# Solution

```

f_A:

if X

if Y

1

else if !Y

Z

endif Y

else if !X

Y

endif X

g:

zero

```

### 6. Boolean Satisfiability (25 points)

In our verification problem, the question that we are trying to answer – namely, whether the circuits are equivalent – has an affirmative answer if equivalence holds for *all* possible input assignments. It has a negative answer if equivalence does not hold for *any* input assignment. So-called SAT-based techniques, based on heuristic solutions to the Boolean satisfiability problem, can be used to answer questions that fit this mold. In theory, such algorithms can take time that is exponential in the number of variables to complete. In practice, they have shown themselves to be remarkably efficient.

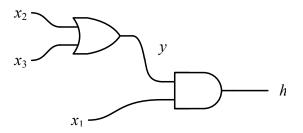

SAT-based analysis begins with a circuit structure and proceeds by packaging the Boolean function that it computes in conjunctive normal form (CNF). This is passed to heuristic algorithms known as SAT solvers. If the solver returns "UNSAT," this means that there is no satisfying assignment to the formula. Otherwise, the solver returns "SAT" along with a satisfying assignment. For instance, consider the circuit in Figure 5. The corresponding CNF formula is:

$$(\bar{x}_2+y)(\bar{x}_3+y)(x_2+x_3+\bar{y})(x_1+\bar{h})(y+\bar{h})(\bar{x}_1+\bar{y}+h)(h).$$

The solver would return SAT. A satisfying assignment for this formula is  $x_1 = x_2 = x_3 = y = h = 1$ .

Figure 5: A circuit illustrating Boolean satisfiability.

Based on the construct in Figure 2, write a CNF formula for the question: are Circuits A and B equivalent?

# Solution

Label the AND gate outputs  $y_1, y_2, y_3$ , and  $z_1, z_2, z_3$ . Label the OR gate outputs  $f_A$  and  $f_B$ . Label the XOR gate output g. Define

$$\begin{array}{rcl} c_1 &=& (X+\bar{y}_1)(Z+\bar{y}_1)(\bar{X}+\bar{Z}+y_1)\\ c_2 &=& (X+\bar{y}_2)(Y+\bar{y}_2)(X+Y+y_2)\\ c_3 &=& (\bar{X}+\bar{y}_3)(Y+\bar{y}_3)(X+\bar{Y}+y_3)\\ c &=& (\bar{y}_1+f_A)(\bar{y}_2+f_A)(\bar{y}_3+f_A)(y_1+y_2+y_3+\bar{f}_A)\\ d_1 &=& (X+\bar{z}_1)(Z+\bar{z}_1)(\bar{X}+\bar{Z}+z_1)\\ d_2 &=& (W+\bar{z}_2)(Y+\bar{z}_2)(\bar{W}+\bar{Y}+z_2)\\ d_3 &=& (\bar{W}+\bar{z}_3)(Y+\bar{z}_3)(W+\bar{Y}+z_3)\\ d &=& (\bar{z}_1+f_B)(\bar{z}_2+f_B)(\bar{z}_3+f_B)(z_1+z_2+z_3+\bar{f}_b)\\ svne &=& (\bar{f}_A+f_B+g)(f_A+\bar{f}_B+g)(f_A+f_B+\bar{g})(\bar{f}_A+\bar{f}_B+\bar{g}). \end{array}$$

The CNF formula is

$$(c_1)(c_2)(c_3)(c)(d_1)(d_2)(d_3)(d)(e)(g)$$